Tổ chức bộ nhớ bán dẫn

Ô nhớ (cell)

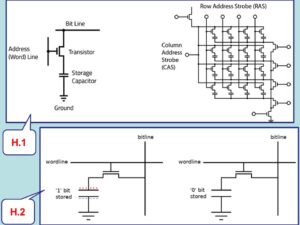

Mỗi ô nhớ được tạo thành từ một tụ điện và một bóng bán dẫn. Tụ điện lưu trữ dữ liệu dưới dạng điện tích với mỗi tụ điện lưu trữ một bit dữ liệu. Hình H.1

Hoạt động của ô nhớ

DRAM là một chip nhớ truy cập ngẫu nhiên để lưu trữ dữ liệu dễ mất trong các ô nhớ và cho phép mật độ cao hơn.

DRAM bao gồm các ô nhớ được cấu hình trong một mảng cột và hàng. Một vi mạch DRAM có thể mang hàng nghìn ô nhớ như vậy.

Mỗi ô nhớ được tạo thành từ một tụ điện và một bóng bán dẫn. Tụ điện lưu trữ dữ liệu dưới dạng điện tích với mỗi tụ điện lưu trữ một bit dữ liệu.

Một câu hỏi đặt ra là tại sao DRAM được coi là Động?

Một RAM động được gọi là động vì nó cần được làm mới liên tục để giữ lại nội dung của nó. Một RAM động được cấu tạo bởi các ô nhớ. Mỗi ô nhớ được làm bằng một khối kép gồm một bóng bán dẫn và một tụ điện. Mỗi tụ điện lưu trữ một bit dữ liệu trong khi bóng bán dẫn khuếch đại hoặc chuyển đổi điện tích.

Các bóng bán dẫn dễ bị rò rỉ và như vậy thường gây ra sự phóng điện dần dần của tụ điện. Sự phóng điện của tụ điện làm cho nó mất thông tin được lưu trữ. Để tránh mất thông tin này, DRAM được làm mới cứ sau vài phần mười giây để bảo toàn dữ liệu. Khi làm mới, chúng ta cung cấp một điện tích mới cho tụ điện.

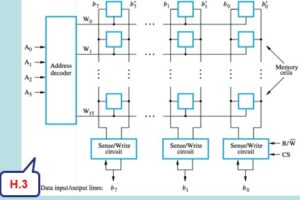

Một vi mạch DRAM được tạo thành từ các ô nhớ, mỗi ô gồm một bóng bán dẫn và một tụ điện. Hình H.2 là Mạch DRAM

Các bóng bán dẫn tích điện và phóng điện tụ điện hoạt động như một công tắc. Khi một điện áp được áp dụng cho đường địa chỉ, bóng bán dẫn cho phép dòng điện chạy như trong một công tắc đóng. Khi không có ứng dụng của điện áp, bóng bán dẫn được coi là một công tắc mở. Tụ điện lưu trữ dữ liệu dưới dạng điện tích. Các ô nhớ được cấu hình trong một mảng cột và hàng. Các cột được gọi là dòng bit trong khi các hàng được gọi là dòng từ. Nơi dòng bit và dòng từ giao nhau được gọi là địa chỉ bộ nhớ. Để hoạt động, một DRAM giải phóng điện tích cho một cột cụ thể. Bóng bán dẫn nằm ở mỗi bit trong cột được kích hoạt.

Qui trình ghi, đọc

Trong quy trình “ghi”, trạng thái của tụ điện được xác định bởi các dòng hàng.

Trong quá trình đọc, mức điện tích của tụ điện được xác định bởi bộ khuếch đại cảm biến. Điều này là do mỗi tụ điện lưu trữ điện tích quá nhỏ để đọc trực tiếp.

Mức điện tích năm mươi phần trăm được đọc là logic “1”. Mức điện tích dưới năm mươi phần trăm được đọc là logic “0”.

Việc đọc từ dòng bit gây ra dòng điện tích ra khỏi tụ điện. Điều này, nếu không được chọn, sẽ dẫn đến mất dữ liệu.

Để trả lại giá trị đọc từ dòng bit vào tụ điện, một thao tác sạc trước được thực hiện.

Thứ tự làm mới được bộ đếm theo dõi theo thứ tự truy cập các hàng.

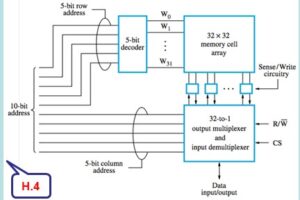

Ví dụ về một mạch tế bào bộ nhớ được tổ chức dưới dạng mảng, một ô lưu trữ một bit thông tin mỗi hàng tạo thành một từ bộ nhớ, tất cả các ô của một hàng được kết nối với một dòng chung (‘dòng từ’) mỗi cột được kết nối với mạch Sense / Write bằng hai dòng bit. Sau đây là một DDR tổ chức 16 x 8 (16 từ, mỗi từ 8 bit):

Mạch tế bào bộ nhớ được tổ chức dưới dạng mảng

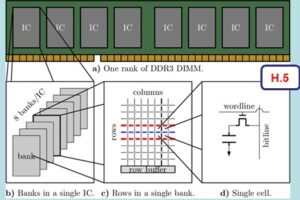

Một mạch tế bào bộ nhớ 1024 được tổ chức theo định dạng 1K x 1 (1000 từ, mỗi từ 1 bit):

Tổ chức một thanh DRAM

DRAM được tổ chức thành các mô-đun trên bo mạch. Mô-đun là một bảng mạch được bố trí các IC DRAM trên đó.

Tổ chức một thanh RAM DDR3

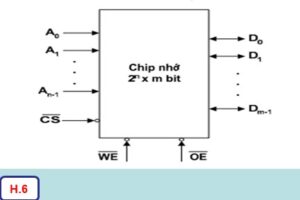

Tổ chức tổng quát chíp nhớ

Các tín hiệu của chíp nhớ.

Các đường địa chỉ: An-1->A0:có 2n từ nhớ

Các đường dữ liệu: Dn-1 ->D0: độ dài từ nhớ bằng m bit

Dung lượng chip nhớ: 2n x m bit

Các đường điều khiển:

Tín hiệu chọn chip CS (Chip Select)

Tín hiệu điều khiển đọc OE(output Enable)

Tín hiệu điều khiển ghi wE(write enable)

Dung lượng chip nhớ=2n xm bit

Cần thiết kế để tăng dung lượng:

Thiết kế tăng độ dài từ nhớ

Thiết kế tăng số lượng từ nhớ

Thiết kế kết hợp